發行人:許聞廉 編:王新民

執行編輯: 黄 琪

The Association for Computational Linguistics and Chinese Language Processing 第二十三卷第三期

E-Mail: aclclp@hp.iis.sinica.edu.tw 地 址:台北市研究院路二段128號中研院資訊所

Website: http://www.aclclp.org.tw 電 話: (02)2788-3799 ext:1502

傳 眞: (02) 2788-1638 劃 撥:19166251

## 本期要目

壹、出席 ACL 2012 心得報告(郭宗廷、張至)

第 2~4 頁

貳、ROCLING 2012 Call for Papers

第5頁

參、專文-模糊類神經處理器之硬體實現(吳俊德、朱振緯)

第6~15頁

### **ROCLING 2012**

「第二十四屆自然語言與語音處理研討會」 由元智大學資訊工程學系、資訊管理學系及本會 共同主辦,謹訂於九月二十一日(星期五)~二十二 日(星期六)假桃園縣中壢市元智大學舉行。本次 會議將廣邀學界與產業界投稿、經嚴謹同儕評審 審稿程序,由學者發表高水準的論文,同時並舉 行國科會研究計畫執行成果發表會,大會分別邀 請到美國 The Association for Computational Linguistics的會長 Dr. Kenneth Church 及微軟研究 院首席研究員 Dr. Li Deng 進行專題演講。會議中 亦將安排時間,讓與會學者以及從事相關研究之 企業廠商進行討論與交流,透過產、學、研各界 分享交流此領域最新的研發成果,藉此帶動自然 語言及語音相關資訊技術的研究與發展,更進一 步促進國內學術機構、工業界與國際間之交流合 作。徵稿啓事請參閱本刊第五頁。

## 獎助學生出席國際會議公告

會議名稱: ACL 2012

獎助學生:張至(清華大學資應所)

論文題目: Learning to Find Translations and

Transliterations on the Web

獎助金額: US\$600 元

計算語言學學會

會議名稱: ACL 2012

獎助學生:郭宗廷(台灣大學網媒所)

論文題目: Exploiting Latent Information to Predict

Diffusions of Novel Topics on Social

Networks

獎助金額: US\$600 元

## 博碩士論文獎開始申請

### 名額及獎項:

- 1. 博士論文優等獎:一名,獎金二萬元,並頒給 學生及指導教授獎狀各乙紙。

- 2. 博士論文佳作獎:一名,獎金一萬元,並頒給 學生及指導教授獎狀各乙紙。

- 3. 碩士論文優等獎:一名,獎金一萬元,並頒給 學生及指導教授獎狀各乙紙。

- 4. 碩士論文佳作獎:三名,獎金各伍仟元,並頒 給學生及指導教授獎狀各乙紙。

### 申請資格:

- 1. 國內大專院校博碩士班應屆畢業生從事計算 語言學相關研究方向者,由其指導教授推薦。

- 2. 參賽限制:每位指導教授以推薦一篇博士論文 及兩篇碩士論文爲限。(含個人指導與共同指 導)。

申請期間:7/1~8/24,申請手續請參閱本會網頁: http://www.aclclp.org.tw/doc/shipreg.htm •

2012年8月6日

## 出席 ACL 2012 心得報告

### 郭宗廷

台灣大學資訊網路與多媒體研究所

### 一、參加會議過程:

ACL 是計算語言學與自然語言處理的頂尖會議之一,全名叫做"The Association for Computational Linguistics"。今年 ACL 2012 第 50 屆舉辦在韓國濟州,long paper 的論文接受率爲 112/571=19%,而 short paper 的論文接受率爲 77/369=20%。我們的論文是 short paper。

ACL 2012 會議行程包括七月八日的 Tutorial,九日到十一日的 Main conference 及十二日到十四日的 Workshop。Main conference 的整體架構包括兩場 Invited talk、一場 Best paper award、Poster 和 Demo 時間及許多場的 sessions。Invited talk 的題目分別爲"Remembrance of ACLs past"及"Computational linguistics: Where do we go from here?",描述了 ACL 整個會議的過去及 NLP 領域相關的未來。今年的 Best paper award 則爲 NTT Lab 的 "Bayesian Symbol – Refined Tree Substitution Grammars for Syntactic Parsing"和 Microsoft Research Asia 的 "String Re-writing Kernel",分別是對於 Parsing tree 作效率上的改良,以及探討句子的詞語順序。

ACL 主要的 sessions 分爲 machine translation`speech`discourse`time`meaning`Chinese lexical processing `lexical semantics`social media`user generated content`multilinguality、topics`name and relation······等,涵蓋的範圍真的很廣。跟我們研究題目比較相關的爲 topic 及 machine learning session,對我們的研究有非常大的幫助。

#### 二、 會議心得:

在整體會議過程中,有許多新的想法及觀點可以讓我們從不同角度切入去重新思考 我們的研究,所以整體而言對我們的研究很有幫助。而且出席 ACL 的與會人員有很多重 量級人物,親眼目睹撰寫課本的教授在面前授課,感覺很不一樣!

今年我們的 short paper 在這個 poster 時段報告。藉由直接和聽眾們的互動,可以互相交流想法。此外,比較幸運的是遇到一些跟我們研究有關的教授,他們也提點我們一些可以往下延伸的方向,雖然其中某些方向我們之前就已經有討論過並且實作了,但還是很感謝他們!能跟來自於不同地方的人做學術上的交流非常愉快,也很有收獲!參加完爲期三天的會議心中真的感觸很多,不同國家、不同學校的討論風氣,或許才是我們真正要學習的一環。

### 三、建議:

無。

## 四、攜回資料名稱及內容:

今年 ACL 2012 會議附件包含一個會議論文之 USB、一本會議議程手冊、一張會議收據、以及一些會議相關文宣。

## 五、 其他:

明年 ACL 2013 將舉辦在保加利亞首都蘇非亞市(Sofia, Bulgaria)。

## 出席 ACL 2012 心得報告

### 張至

清華大學資訊系統與應用研究所

The Annual Meeting of the Association for Computational Linguistics (ACL) 會議是自然語言處理領域最頂尖的國際研討會,吸引非常多各國的學者以及相關產業參加。本人於2012年7月8日晚間抵達韓國濟州島,並於隔日一早前往International Conference Center (ICC) 參加第50屆的ACL會議(ACL 2012)。這次會議一共三日,我們的論文被安排於第三日下午進行報告。會議結束後,於15日返回台灣。從閉幕式的投影片得知,今年一共有超過900的自然語言處理、資訊檢索、語音處理研究之研究人員參加這一場盛會;產業界的參與也很熱烈,會場內看到許多歐美以及日韓的公司參與及贊助,如百度、Google、微軟、ETS、樂天研究院、LG等知名公司。

許多自然語言處理的會議常邀請相關的其他領域學者來進行 keynote 演講,而 ACL 也不例外。今年是會議的五十周年,keynote 演講請到了於 University of Pennsylvania 研究計算與認知學的 Aravind K. Joshi 教授,以他的個人觀點來回顧這五十年間自然語言處理的發展,並討論了許多自然語言處理草創之初所提出的方法。演講內容輕鬆有趣,讓我們了解了自然語言處理這個領域的起源與歷史。

三天的會議共分了五個平行進行的議程,議題非常廣泛,而報告也都很清楚且精采, 讓年輕的研究者們可以在這短短三天內,了解各個研究議題的現況與可能的未來發展方向, 也能發掘許多有趣的新論文可在回國後好好研讀。

會議的前兩天除專心聽講外,也花了一些時間來演練講稿,並於第三日順利完成報告。 ACL 會議無論是報告後的問題時間或是海報議程,來自各地的學者都非常踴躍的互相討 論與提問。我在報告完後也接受了四五個問題。除了提出問題外,也有學者建議我除了做 自動與人工的評估外,也可以針對實驗產生的輸出的多樣性,做更進一步的研究。整體而 言,此次參與會議的三日非常充實,無論是聽取報告,休息時間與其他學者的互動,或是 第三日的口頭報告與問答都令我獲益良多。

# Call for Papers The 24<sup>th</sup> Conference on Computational Linguistics and Speech Processing (ROCLING 2012)

September 21-22, 2012, Chung-Li, Taiwan https://sites.google.com/site/rocling12/

The 24th Conference on Computational Linguistics and Speech Processing (ROCLING 2012) will be held at Yuan Ze University, Chung-Li, Taiwan, 21-22 September 2012. Sponsored by the Association for Computational Linguistics and Chinese Language Processing (ACLCLP), ROCLING is the most historied and comprehensive conference focused on computational linguistics, speech processing, and related areas in Taiwan. ROCLING 2012 will be co-hosted by the Department of Information Management and the Department of Computer Science and Engineering, Yuan Ze University. The two-day conference will feature a full complement of invited talks, paper and poster sessions. ROCLING 2012 invites submissions of original and unpublished research papers on all areas of computational linguistics and speech processing, including but not limited to:

- cognitive/psychological linguistics

- discourse/dialogue modeling

- information extraction/text mining

- information retrieval

- language understanding/generation

- lexicon/morphology

- machine translation/multilingual processing

- named entity recognition

- NLP applications/tools/resources

- phonetics/phonology

- question answering

- semantic web

- semantics/pragmatics

- speech analysis/synthesis

- speech recognition/understanding

- spoken dialog systems

- spoken language processing

- syntax/parsing

- text/speech summarization

- web knowledge discovery

- word segmentation/POS tagging

- others

### **Important Dates:**

Submission due: August 10, 2012

Notification of acceptance: August 26, 2012

Camera-ready due: September 2, 2012

Conference date: September 21 - 22, 2012

### **Kevnotes:**

Dr. Kenneth Church, President of ACL

Dr. Li Deng, Principal Researcher, Microsoft Research

# 模糊類神經處理器之硬體實現 Hardware Implementation of Fuzzy-Neural-Processor

吳俊德 教授,朱振緯 博士 國立暨南國際大學電機工程學系 ginderwu@ncnu.edu.tw

### 摘要

模糊類神經網路結合了「模糊推論的處理不確定性能力」與「類神經網路的自我學習能力」,它已經成功地被運用於語音辨識。這啟發我們提出以模糊類神經網路爲基礎的處理器去執行語音辨識相關模組。本論文提出模糊類神經處理器的硬體實現。爲實現模糊推論指令,我們將採用軟硬體共同設計方法:微積分的連鎖律被應用於更新模糊網路的權重,而模糊推論指令能實現非線性函數以模擬人腦的決策。然後我們整合模糊網路硬體與高效能處理器的架構以建立一個模糊推論型處理器。所得之晶片採用四層管線式架構以進一步增加效能,此發展的晶片相信能使語音辨識功能更有效率地整合於現今智慧型手機中、達到低複雜度的具體目標。

關鍵詞:模糊類神經處理器、軟硬體共同設計、連鎖律、非線性函數、管線式架構。

## 1. 簡介

個人電腦處理器核心為算術邏輯運算單元(ALU),其功能完全是由處理記憶體上的 0 與 1 所造成的「符號運算」(symbolic computing)。然而人腦具備學習以往的經驗來預測出下一步可能的狀況,採用推論估測手段來取代大量的符號運算。以股票交易為例,人腦根據歷史資料與財報數據作經驗法則來推論最佳的下一步決策。由此可以發現現今電腦架構中缺少推論型態的指令集功能。模糊推論型處理器可估測或推論非線性函數,因此它可以模擬人腦採用推論估測手段來取代大量的符號運算。在另一方面,可攜式電子產品技術近年來不斷地進步,使得嵌入式多媒體系統晶片的需求也越來越多。因此,友善的人機溝通介面設計也會越來越重要。人機介面設計的目標是使用者能容易學習上手,並掌控資料的處理狀況。本文所提出的模糊推論型處理器將採取軟硬體共同設計(Software/ Hardware Codesign)方法[1]。雖然[2]利用 8051 實現嵌入式系統設計,但由於僅含 8 位元的處理器、128Bytes 內部資料記憶體以及 4KB 的內部程式記憶體,這樣陽春型的運算能力使 8051 處理器不適用來處理龐大的計算,因此無法應用在較複雜的語音演算法。業界有以 Motorola DSP56000 為主要運算核心並採用軟硬體共同設計方式[3]。[4]則是以數個 API 為核心設計而成的辨識系統。[5,6]是以 DSP 之套件實現其所研究。一般來說, DSP 處理器很適合用於執行大量的運算,處理的效能相當地快速。但現階段市面上的公司所銷售的 DSP 晶片

(TI或 ADI)價格昂貴。除此之外,若晶片的功率消耗高也易造成系統待機時間短。基於以 上各種原因,我們希望透過自行研發低功率、高運算能力模糊推論型處理器晶片來加速此 類商品應用化。

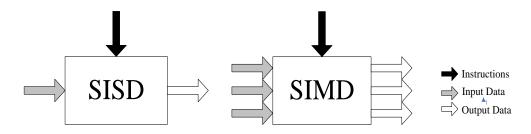

圖 1、SISD 與 SIMD

處理器按照市場上的需求,可以分爲兩類。第一類需求,應用領域爲廉價的、大規模 嵌入式應用系統,如手機、伺服電機控制以及可攜式數位音頻播放器等。另一類需求則是 需要用複雜運算法對大量數據進行處理的應用,例如 3D 影像處理和多聲道音訊處理等。 在圖 1 中,SISD (Single Instruction Single Data)的意義是「單指令,單資料流」。例如一般的 整數/浮點運算單元,都是輸入一筆指令,處理一筆資料,輸出一個結果。SIMD (Single Instruction, Multiple Data)的意義是「單指令,多資料流」,也就是一個指令同時對多個資料 進行相同的處理動作。SIMD 又可以稱作向量運算器,在面對一串的資料同時運算時,可以 對「同樣運算」一次處理多筆資料。例如像 3D Gaming 的矩陣轉換、矩陣運算或 DSP 運 算的 Convolution 等。爲了達成多媒體處理速度上的需求,某些處理器採用超長指令字 VLIW (Very Long Instruction Word)架構,在此架構中,單個周期時間內可以實現多個指令 以滿足多媒體訊號平行處理需求。然而 VLIW 架構受限於程式的相容性,因此一般處理器 很少去強調平行處理的概念。德州儀器成功地將 VLIW 的架構實現於需要講求效能的 DSP 上,並廣泛地應用於多媒體系統中。它以簡易的方式達到平行處理的目的,更重要的是在 講求效能的數位訊號處理上,韌體開發者大都會針對特定處理器指令,把程式碼進行最佳 化排程,以達到最好的執行效能。因此,相較於大型電腦的程式開發者不會去在意程式碼 的平行度,數位訊號處理器的程式開發人員會刻意將程式碼做調整以達到最大的指令平行 度,以充分利用 VLIW 架構處理器指令集的特點。在現今講求高效能程式設計中具有相當 優勢。表 1 列出目前兩顆以 VLIW 爲架構的常見 DSP 處理器。

**TI TMS320C62X** ADI TigerSHARC 運算法格式 Fixed-Point Fixed-Point Data width 32-bit 32-bit

128

表1、具有VLIW架構的常見DSP處理器

256

項目

**VLIW** Engine

本研究爲實現處理器晶片[7-10],電路使用 Verilog 硬體描述語言設計。晶片製作採用國家晶片系統設計中心(National Chip Implementation Center, CIC)所提供的 cell-based IC design flow。我們可以利用此模糊類神經網路爲基礎之處理器的非線性指令集,撰寫語音辨識演算法。

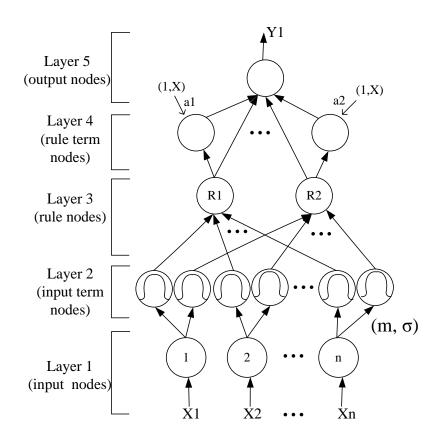

圖 2、類神經網路示意圖

## 2. 模糊類神經演算法

在初始的模糊類神經網路中,是不包含任何規則在其中。其規則是經由網路的學習產生。圖2是模糊類神經網路的示意圖。其中包含了五層架構。其 fuzzy model 可表示如下:

Rule

$$i$$

: IF  $x_1$  is  $A_{i1}$  and ... and  $x_n$  is  $A_{in}$

THEN  $y$  is  $a_{i0} + a_{i1}x_1 + ... + a_{in}x_n$

其中 $x_j$   $(1 \le j \le n)$  是輸入値,y 是輸出値, $a_{ij}$  爲 y 的線性組合參數。接下來我們介紹網路的每一層變化。下面是每一層的輸出

$$f[u_1^{(k)}, u_2^{(k)}, ..., u_p^{(k)}]$$

其中 $u_1^{(k)}, u_2^{(k)}, ..., u_p^{(k)}$ 爲每一個 node 的輸入,k 代表此函數變化是屬於哪一層。

每一層的輸出函數可表示如下:

$$o_i^{(k)} = a(net - input) = a(f)$$

其中 a(.)為 activation function。接下來我們將每層分別作解釋:

第一層:本層中每一個 node 會將輸入的值直接傳送給輸出

$$f = u_i^{(1)}$$

and  $a = f$  (1)

第二層: 在本層裡每一個 node 都代表一個第一層輸入的 linguistic label,此層的函數轉換 為高斯函數:

$$f = -\frac{(u_i^{(2)} - m_{ij})^2}{\sigma_{ii}^2}$$

and  $a = e^f$  (2)

其中 $m_{ii}$ 與 $\sigma_{ii}$ 爲高斯函數的中心和寬度。

第三層:本層為模糊理論中的 precondition matching。因此我們做 AND 運算如下:

$$f = \prod_{i=1}^{p} u_i^{(3)}$$

and  $a = f$  (3)

此層的輸出爲模糊理論中的發射強度。

第四層: 在本層中每一個 node 爲輸入與輸出的線性組合:

$$f = a_{i0} + \sum_{i} a_{ij} x_{j}$$

and  $a = \sum_{i} u_{i}^{(4)} f$  (4)

第五層:本層爲網路的輸出層,其動作爲解模糊化,函數如下:

$$f = \frac{u^{(4)}}{\sum_{i} u_i^{(3)}} \text{ and } a = f$$

(5)

## 3. 模糊類神經網路電路

模糊類神經處理器是以 Takagi-Sugeno-Kang(TS) type 為基礎。它利用最陡坡度法(The Gradient Steepest Descent Method) 反覆地調節網路的連接加權值,並產生模糊規則庫。目標為將實際輸出與期望輸出的誤差函數予以最小化。

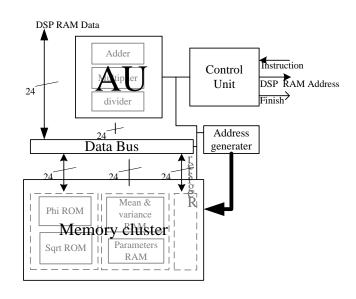

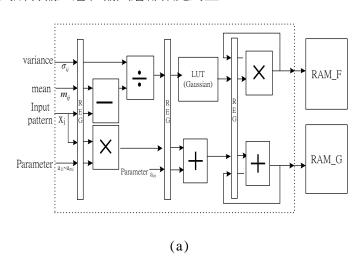

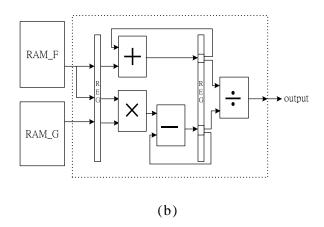

圖 3、模糊類神經架構

圖 3 爲整個模糊類神經的架構圖。它是以記憶體爲主要架構。把所有所需調整的類神經參數(如 mean, variance 等)存在內建的記憶體裡。而爲了提升硬體電路執行效能,我們使用管線式的概念設計。其中分爲兩階段:模糊化以及解模糊化。圖 4 爲兩種架構的示意圖。在第一階段模糊化架構執行完畢後會將資訊存入 RAM\_F 以及 RAM\_G 裡,並且執行解模糊化動作直到所有輸入層和輸出層都做完爲止。

圖 4、(a)模糊化架構(b)解模糊化架構

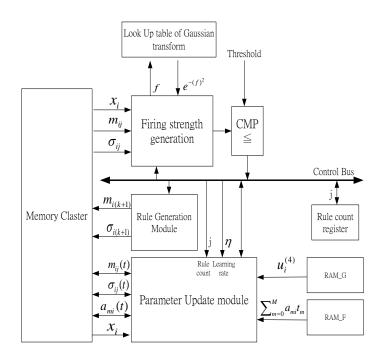

圖 5、學習架構

圖 5 爲整個學習架構的示意圖。其中 fire strength 功能爲產生模組,規則庫產生模組以及參數調整模組。利用此調整架構可以使得整個網路具有彈性可調變的能力。相同地,本架構中所有參數會從內建的記憶體取出做訓練並存回更新數值。

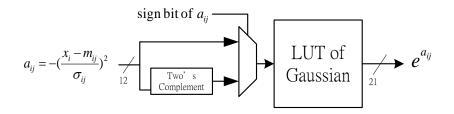

在本電路中,我們大量使用了查表法(LUT)電路,其是使用 cic 所提供的 cell-library 所產生。使用 LUT 方法可大量減少運算時間且增加電路的精準度。為了計算 ROM 的大小,我們定義以下

$$LUT_{size} = LUT_{amount} \times length_{ROM\_output}$$

(6)

$$LUT_{amount} = \frac{b1 - b2}{\Delta x} \tag{7}$$

其中 b1 和 b2 是表的上界和下界, $\Delta x$  是 sample 的距離。圖 6 爲查表法的電路。在此我們定義輸入的範圍爲  $0\sim2^2-1$ , $\Delta x$  爲  $2^{-10}$ (刪除  $2^{-11}$  後面的小數點),因此總共大小爲

$LUT_{size} = LUT_{amount} \times length_{ROM-output} = \{((2^2/2^{-10}) \times 21)/8 \times 1024\} Kbyte = 10.5 Kbyte$

圖 6、查表法電路

## 4. 高效能處理器

本章介紹新發展之高效能處理器、以搭配前述的模糊類神經網路電路,其設計架構概念如下。

高效能處理器晶片架構設計主要分為處理器核心設計與周圍電路設計。在此,我們將專注於核心架構之設計。晶片核心設計將會分割為控制單元、計算單元、資料暫存器、記憶體位置產生器。本處理器將會以四層管線架構(pipeline)設計以增強執行效能。每個指令長度為32 位元,總共可支援14 種定址模式。

### 管線式架構:

我們將採用4層管線處理架構來運作。執行可分爲四階段:

- 1. 取出指令(IF): 此階段從 Program memory 讀出指令進晶片內的指令暫存器。

- 2. 指令解碼(ID): 此階段將指令解碼,從暫存器或是記憶體讀取運算元,並產生訊號來控制指令運算。

- 3. 執行指令(EX):此階段為執行指令。在單一週期內執行完成運算元。

- 4. 儲存結果(W): 此階段會將運算之結果回存回暫存器。

### 定址模式

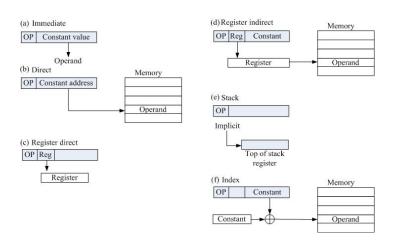

將運算元從資料記憶體中取出時,處理器必須先產生出記憶體之位置。本文所規劃的定址模式包含:直接定址(direct)、立即定址(immediate)、暫存器直接定址(register direct)、暫存器間接定址(register indirect)、索引定址(index)、堆疊定址(stack)。這些定址模式示意圖如圖7所示。

圖 7、定址模式。

## 5. 模糊型指令集規劃

在這裡,我們將模糊類神經網路設計成特別的指令集,基本上可分成四種格式執行: (1) 學習/回想、(2)類神經層的數量、(3)網路的節點、(4)學習速率。控制系統從程式記憶體中接收網路組態設定。同時,控制系統會更新網路結構。學習/回想指令集使用語法如下:

FNNL #N1, #N2, #N3, #N4

FNNT #N1, #N2

其中 FNNL 為學習指令集,四個可調參數分別為輸入層數量、輸出層數量、訓練資料數量以及收斂次數。FNNT 為回想指令,兩個參數分別為輸入以及輸出層數量。表 2 為兩種指令集的機械碼配置。其中第一欄為模糊行指令的 OP,最後一欄為辨別回想以及訓練。

| learning Op L |      |    |                  |                   |                         |                 |   |

|---------------|------|----|------------------|-------------------|-------------------------|-----------------|---|

| 39            | 3    | 6  | 35 29            | 28 22             | 21 12                   | 11 1            | 0 |

| 1             | 1010 |    | input node count | output node count | Training data count #N3 | Iteration count | 0 |

|               |      |    | #N1              | #N2               |                         | #N4             | Ш |

| Testing Op L  |      |    |                  |                   |                         |                 |   |

| 39            |      | 36 | 35 29            | 28 22             | 21                      | 1               | 0 |

| 1             | 1010 |    | input node count | output node count | No use                  |                 | 1 |

|               |      |    | #N1              | #N2               |                         |                 | Ш |

表 2、模糊類神經網路指令集格式

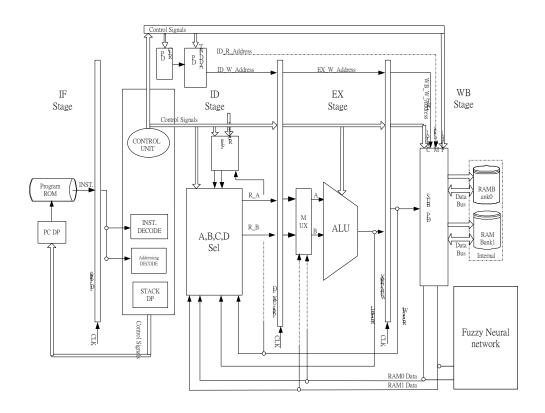

圖 8、模糊類神經處理器示意圖

圖 8 爲整個模糊類神經處理器電路示意圖。爲了實現模糊推論型處理器,我們將模糊類神經網路與高效能處理器進行整合,以使此晶片具備非線性推論型態的指令集功能。指令集儲存於指令記憶體(program ROM)中。處理器藉由讀取上述之指令集來修改內部的模糊類神經網路模式。設定模糊類神經網路模式後,會將更新的資料儲存至晶片暫存器中。

## 6. 結論

本文主要內容在於,介紹我們所新發展之整合模糊類神經網路硬體與中央處理器,進而建立一個模糊類神經處理器。藉由軟硬體共同設計方法實現模糊推論型處理器,它可估測或推論非線性函數,因此它可以模擬人腦採用推論估測手段來取代大量的符號運算。爲增加執行效能,此晶片採用四層管線式架構。藉由此模糊類神經網路爲基礎之處理器的非線性指令集,我們可以撰寫其對應的語音辨識演算法,所發展的系統與晶片相對於建立在執行一般功能的處理器(processor)的系統而言,能使語音辨識功能更有效率地實現。

## 7. 參考文獻

- [1] Di Nuovo, Palesi M. and Patti D., "Fuzzy decision making in embedded system design," Hardware/Software Codesign and System Synthesis, 2006. CODES+ISSS '06. Proceedings of the 4th International Conference, vol., no., pp.223-228, 22-25 Oct. 2006

- [2] Bo Cui and Tongze Xue, "Design and realization of an intelligent access control system based on voice recognition," Computing, Communication, Control, and Management, 2009. CCCM 2009. ISECS International Colloquium on , vol.1, no., pp.229-232, 8-9 Aug. 2009

- [3] Bakhti, A. and Benbaouche, L., "Simulink-DSP Co-Design of a Fuzzy Logic Controller," IEEE Industrial Electronics, IECON 2006 32nd Annual Conference on , vol., no., pp.4587-4592, 6-10 Nov. 2006

- [4] Unsang Park, Yiying Tong and Jain, A.K., "Face recognition with temporal invariance: A 3D aging model," Automatic Face & Gesture Recognition, 2008. FG '08. 8th IEEE International Conference on , vol., no., pp.1-7, 17-19 Sept. 2008

- [5] Shi J. and Lee W.S., "An experimental comparison of a model based controller and a fuzzy logic controller for magnetic bearing system stabilization," Control and Automation, 2009. ICCA 2009. IEEE International Conference on , vol., no., pp.379-384, 9-11 Dec. 2009

- [6] Chun Wan and Lili Liu, "Research of speech emotion recognition based on embedded system," Computer Science and Education (ICCSE), 2010 5th International Conference on, vol., no., pp.1129-1133, 24-27 Aug. 2010

- [7] J. F. Wang, J. C. Wang, H. C. Chen, T. L. Chen, C. C. Chang and M. C. Shih, "Chip design of portable speech memopad suitable for persons with visual disabilities," *IEEE Transactions on Speech and Audio Processing*, vol. 10, Issue 8, pp.644-658, Nov. 2002.

- [8] J. C. Wang, J. F. Wang and H. C. Chen, "Single chip implementation of the 1.6 kbps speech vocoder," *Proceedings of IEEE international Symposium on Circuits and System*, vol.5, pp.597 600, May 2000.

- [9] A. N. Suen, J. F. Wang and Y. L. Chiang, "A cepstrum chip: architecture and implementation," *IEEE International Symposium on Circuits and Systems*, pp.1428 - 1431 vol.2, May 1995.

- [10] S. N. Kim, I. C. Hwang, Y. W. Kim and S. W. Kim, "A VLSI chip for isolated speech recognition system," *IEEE Transaction on Consumer Electronics*, vol. 42, Issue: 3, pp.458-467, Aug, 1996.